# Chapter 21: Serial Ports

Traditionally, serial communications has been the long distance choice—the best and sometimes only way of getting your message out. Recent advances in technology and standardization have made serial links the new choice for tying your PC to its peripherals. In coming years, serial communication may become synonymous with PC expansion.[/block]

- Background

- Clocking

- Frames

- Packets

- Background

- Error Handling

- <u>History</u>

- <u>RS-232C</u>

- <u>Electrical Operation</u>

- Connectors

- <u>25-Pin</u>

- <u>9-Pin</u>

- Motherboard Headers

- <u>Signals</u>

- <u>Definitions</u>

- <u>Cables</u>

- <u>Straight Through Cables</u>

- Adapter Cables

- <u>Crossover Cables</u>

- <u>UARTs</u>

- <u>8250</u>

- <u>16450</u>

- <u>16550A</u>

- <u>Register Function</u>

- Buffer Control

- Identifying UARTs

- Enhanced Serial Ports

- Logical Interface

- Port Names

- Interrupts

- <u>ACCESS.bus</u>

- Architecture

- <u>Signaling</u>

- Transfers

- Arbitration

- Messages

- Addresses

- <u>Connections</u>

- <u>IrDA</u>

- <u>History</u>

- Overview

- Physical Layer

- Infrared Light

- Data Rates

- Pulse Width

- Modulation

- <u>Bit Stuffing</u>

- Format

- <u>Aborted Frames</u>

- Interference Suppression

- Link Access Protocol

- Primary and Secondary Stations

- Frame Types

- Addressing

- Error Detection

- Link Management Protocol

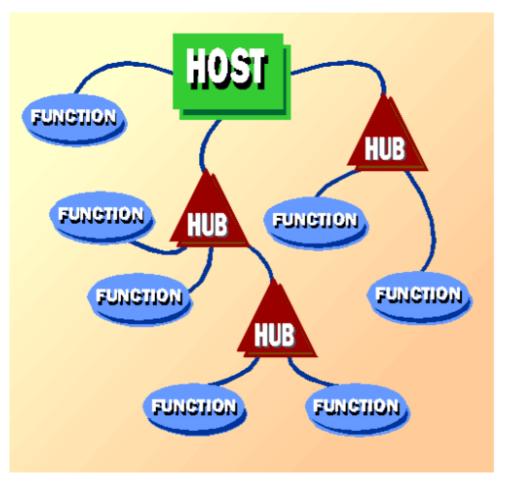

- Universal Serial Bus

- Background

- Connectors

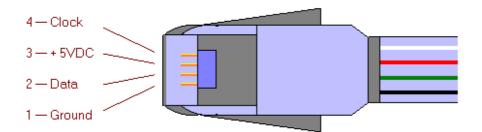

- <u>Cable</u>

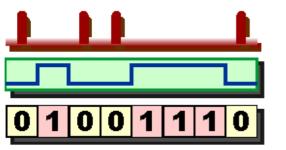

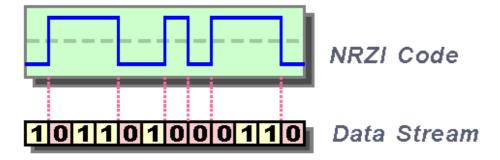

- Data Coding

- Protocol

- <u>Token Packets</u>

- Data Packets

- Handshake Packets

- <u>IEEE-1394</u>

- Background

- Performance

- Timing

- <u>Setup</u>

- <u>Arbitration</u>

- <u>Architecture</u>

- Bus Management Layer

- Transaction Layer

- Link Layer

- Physical Layer

- Cabling

# 21

# **Serial Ports**

For almost two decades, the serial port has been the least common denominator of computer communications, an escape route for your long distance messages but one burdened by its own ball and chain. Today that situation is changing. Where once there was but one "serial port," today several serial communication standards vie for your attention.

Serial communication once hobbled your PC with data rates out of the dark ages. The classic serial port was a carryover from a previous generation of technology. Its low speed was a sad match for the quick pulse of the PC. It was like having a medieval scribe ink out your PC's owner's manual in glorious Gothic script, a trial of your patience that took little advantage of current technology. (Then again, some PC documentation arrives so late you just *might* suspect some scribe to be scrawling it out with quill and oxgall ink.) While PCs generated millions of characters per second, classic serial ports doled out a few hundred or thousand in the same time.

New serial technologies kick communications back into high gear. They are quick enough not only to transfer text messages but to move your voice digitally or even handle full motion video in real time. The also add the versatility of going wireless so you don't have to tie yourself to your desk with a tangle of communications cables.

Today engineers have five chief choices for serial communications between your PC and other devices. The classic serial port (best known by its official EIA standard designation, RS-232C), ACCESS.bus, the IrDA optical connection, the Universal Serial Bus, and P1394.

The least common denominator is the RS-232C port, standard equipment on nearly every PC since 1984. Throughout the first decade and a half of personal computing, serial port meant only RS-232C. But the standard is even older than the first PCs, having been a telephone system standard long before. And, like most of the carryovers from early technology, RS-232C brought its own baggage—a speed limit more severe than a stern first grade teacher who believes that rulers are for discipline rather than measurement.

ACCESS.bus is an inexpensive but low speed serial connection to link multiple undemanding devices with your PC. Rather than speed, its advantage over RS-232C is versatility. It can connect more devices to your PC than all the RS-232C ports you or your system could stand. Moreover, it is a simple standard, one without a confusion of cables and connectors.

IrDA gives the RS-232C standard a new medium, sending signals through the air instead of wires. Using infrared signals exactly like those of television remote controls, IrDA allows you to transfer files between your notebook and desktop PC without wrestling with a cable connection. If the relatively new standard takes hold, you may also link your notebook PC to your printer or other peripherals with invisible light beams. The principal drawback is IrDA's RS-232C heritage. The maximum IrDA data rate matches the low speed of the RS-232C signals.

Universal Serial Bus is the PC generation's answer to serial communications. Unlike the RS-232C based serial systems that are designed to link two devices, USB acts as a true bus that can link as many as 127 devices to your PC without worries about matching connectors and cables (although it remains a wire based design). Speed takes a quantum leap over RS-232C with a peak data rate of 12 megabits per second as well as a low speed mode that operates at 1.5 megabits per second. In order to make the "universal" in the name a reality, the design goal of the new standard aims low: USB was designed to be a low cost interface, cheap enough for every PC.

P1394 pushes serial technology further still, with a maximum data rate of 100 megabits per second currently and rates as high as 400 megabits per second envisioned. More expensive to implement than USB, it fits with the new SCSI-3 scheme of things and

offers a reliable means of linking high speed peripherals such as hard disks and real time video systems to PCs. Table 21.1 compares the characteristics of some of the most common serial port standards.

| Standard   | Data rate (current) | Medium                | Devices per port |

|------------|---------------------|-----------------------|------------------|

| RS-232C    | 115,200 bps         | Twisted pair          | 1                |

| ACCESS.bus | 100 Kbps            | 4-wire shielded cable | 125              |

| IrDA       | 4 Mbps              | Optical               | 126              |

| USB        | 12 Mbps             | Special 4-wire cable  | 127              |

| IEEE 1394  | 100 Mbps            | Special 6-wire cable  | 16               |

#### **Table 21.1. A Comparison of Serial Interfaces**

Despite the differences among these standards, all have a common basis. They treat data one-dimensionally, as a long stream or series of bits. From this common ground, each goes its own direction. At heart, however, all involve the same repackaging of data to make it fit a channel with a single stream of data.

# Background

No matter the name and standard, all serial ports are the same, at least functionally. Each takes the 8, 16, or 32 parallel bits your computer exchanges across its data bus and turns them sideways—from a broadside of digital blips into a pulse chain that can walk the plank, single file. This form of communication earns its name "serial" because the individual bits of information are transferred in a long series.

The change marks a significant difference in coding. The bits of parallel data are coded by their position. That is, the designation of the bus line they travel confers value. The most significant bit travels down the line designated for the most significant signal. With a serial port, the significance is awarded by timing. The position of a bit in a pulse string gives it its value. The later in the string, the more important the bit.

In a perfect world, a single circuit—nothing more than two wires, a signal line and a ground—would be all that was necessary to move this serial signal from one place to another without further ado. Of course, a perfect world would also have fairies and other benevolent spirits to help usher the data along and protect it from all the evil imps and energies lurking about trying to debase and disgrace the singular purity of serial transfer.

The world is, alas, not perfect, and the world of computers even less so. Many misfortunes can befall the vulnerable serial data bit as it crawls through its connection. One of the bits of a full byte of data may go astray, leaving a piece of data with a smaller value on arrival than it had at departure—a problem akin to shipping alcohol by a courier service operated by dipsomaniacs. With the vacancy in the data stream, all the other bits will slip up a place and assume new values. Or the opposite case—in the spirit of electronic camaraderie, an otherwise well meaning signal might adopt a stray bit like a child takes on a kitten, only to later discover the miracle of pregnancy and a progeny of errors that ripple through the communications stream, pushing all the bits backward. In either case, the prognosis is not good. With this elementary form of serial communications, one mistaken bit either way, and every byte that follows will be in error.

Establishing reliable serial communications means overcoming these bit error problems and many others as well. Thanks to some digital ingenuity, however, serial communications work and work well—well enough that you and your PC can depend on them.

# Clocking

In computers, a serial signal is one in which the bits of data of the digital code are arranged in a series. They travel through their medium or connection one after another as a train of pulses. Put another way, the pattern that makes up the digital code stretches across the dimension of time rather than across the width of a data bus. Instead of the bits of the digital code getting their significance from their physical position in the lines of the data bus, the get their meaning from their position in time. Instead of traveling through eight distinct connections, a byte of data, for example, makes up a sequence of eight pulses in a serial communications system. Plot signal to time, and the serial connections turns things sideways from the way they would be inside your PC.

Do you detect a pattern here? Time, time, time. Serial ports make data communications a matter of timing. Defining and keeping time become critical issues in serial data exchanges.

Engineers split the universe of serial communications into two distinct forms, synchronous and asynchronous. The difference between them relates to how they deal with time.

*Synchronous communications* require the sending and receiving system—for our purposes, the PC and printer—to synchronize their actions. They share a common time base, a serial *clock*. This clock signal is passed between the two systems either as a

separate signal or by using the pulses of data in the data stream to define it. The serial transmitter and receiver can unambiguously identify each bit in the data stream by its relationship to the shared clock. Because each uses exactly the same clock, they can make the match based on timing alone.

In *asynchronous communications* the transmitter and receiver use separate clocks. Although the two clocks are supposed to be running at the same speed, they don't necessarily tell the same time. They are like your wristwatch and the clock on the town square. One or the other may be a few minutes faster even though both operate at essentially the same speed: a day has 24 hours for both.

An asynchronous communications system also relies on the timing of pulses to define the digital code. But they cannot look to their clocks for infallible guidance. A small error in timing can shift a bit a few positions, say from the least significant place to the most significant, which can drastically affect the meaning of the digital message.

If you've ever had a clock that kept bad time—for example, the CMOS clock inside your PC—you probably noticed that time errors are cumulative. They add up. If your clock is a minute off today, it will be two minutes off tomorrow. The longer time elapses, the more the difference in two clocks will be apparent. The corollary is also true: if you make a comparison over a short enough period, you won't notice a shift between two clocks even if they are running at quite different speeds.

Asynchronous communications banks on this fine slicing of time. By keeping intervals short, they can make two unsynchronized clocks act as if they were synchronized. The otherwise unsynchronized signals can identify the time relationships in the bits of a serial code.

*Isochronous communications* involve time critical data. Your PC uses information that is transferred isochronously in real time. That is, the data are meant for immediate display, typically in a continuous stream. The most common examples are video image data that must be displayed at the proper rate for smooth full motion video and digital audio data that produces sound. Isochronous transmissions may be made using any signaling scheme, be it synchronous or asynchronous. They usually differ from ordinary data transfers in that the system tolerates data errors. It compromises accuracy for the proper timing of information. Whereas error correction in a conventional data transfer may require the retransmission of packets containing errors, an isochronous transfer lets the errors pass through uncorrected. The underlying philosophy is that a bad pixel in an image is less objectionable than image frames that jerk because the flow of the data stream stops for the retransmission of bad packets.

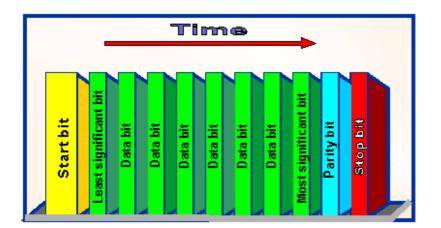

### **Frames**

The basic element of digital information in a serial communication system is the data *frame*. Think of the word as a time frame, the frame bracketing the information like a frame surrounds a window. The bits of the digital code are assigned their value in accordance with their position in the frame. In a synchronous serial communications system, the frame contains the bits of a digital code word. In asynchronous serial communications, the frame also contains a word of data, but it has a greater significance. It is also the time interval in which the clocks of the sending and receiving systems are assumed to be synchronized.

When an asynchronous receiver detects the start of a frame, it resets its clock and then uses its clock to define the significance of each bit in the digital code within the frame. At the start of the next frame, it resets its clock and starts timing the bits again.

The only problem with this system is that an asynchronous receiver needs to know when a frame begins and ends. Synchronous receivers can always look to the clock to know, but the asynchronous system has no such luxury. The trick to making asynchronous communications work is unambiguously defining the frame. Today's asynchronous systems use *start bits* to mark the beginning of a frame and *stop bits* to mark its end. In the middle are a group of *data bits*.

The start bit helps the asynchronous receiver find data in a sea of noise. In some systems, the start bit is given a special identity. In most asynchronous systems, it is twice the length of the other bits inside the frame. In others, the appearance of the bit itself is sufficient. After all, without data, you would expect no pulses. When any pulse pops up, you might expect it to be a start bit.

Each frame ends with one or more stop bits. They assure the receiver that the data in the frame is complete. Most asynchronous communication systems allow for one, one and a half, or two stop bits. Most systems use one because that length makes each frame shorter (which, in turn, means that it takes a shorter time to transmit).

The number of data bits in a frame varies widely. In most asynchronous systems, there will be from five to eight bits of data in each frame. If you plan to use a serial port to connect a modern serial device to your PC, your choices will usually be to use either seven bits or eight bits, the latter being the most popular.

In addition, the data bits in the frame may be augmented by error correction information called a parity bit, which fits between the last bit of data and the stop bit. In modern serial systems, any of five varieties of parity bits are sometimes used: odd, even, space, mark, and none.

The value of the parity bit is keyed to the data bits. The serial transmitter counts the number of digital ones in the data bits and determines whether this total is odd or even. In the odd parity scheme, the transmitter will turn on the parity bit (making it a digital one) only if the total number of digital ones in the data bits is odd. In even priority

systems, the parity bit is set as one only if the data bits contain an even number of digital ones. In mark parity, the parity bit is always a mark, a digital one. In space parity, the parity bit is always a space, a digital zero. With no parity, no parity bit is included in the digital frames, and the stop bits immediately follow the data bits.

By convention, the bits of serial data in each frame are sent least significant bit first. Subsequent bits follow in order of increasing significance. Figure 21.1 illustrates the contents of a single data frame that uses eight data bits and a single stop bit.

#### Figure 21.1 A serial data frame with eight data bits and one stop bit.

# **Packets**

A frame corresponds to a single character. Taken alone, that's not a whole lot of information. A single character rarely suffices for anything except answering multiple choice tests. To make something meaningful, you combine a sequence of characters to form words and sentences.

The serial communications equivalent of a sentence is a *packet*. A packet is a standardized group of characters or frames that makes up the smallest unit that conveys information through the communications system.

# Background

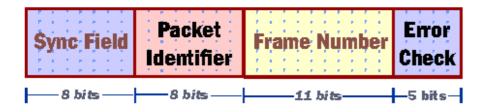

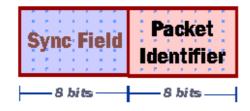

As the name implies, a packet is a container for a message, like a diplomatic packet or envelope. The packet holds the data. In addition, in most packetized systems, the packet also includes an address and, often, a description of its contents. Packets may also include extra data to assure the integrity of their contents—for example, an error detection or error correction scheme of some sort. Figure 21.2 shows a graphical representation of the constituents of a data packet.

### Figure 21.2 Constituents of a typical data packet.

The exact constituents of a packet depend on the communication protocol. In general, however, all packets have much the same construction. They begin with a symbol or character string that allows systems listening in to the communication channel to recognize the bit pattern that follows as a packet.

Each packet bears an address that tells where it is bound. Devices listening in on the communication channel check the address. If it does not match their own or does not indicate that the packet is being broadcast to all devices—in other words, the packet wears an address equivalent to "occupant"—the device ignores the rest of the packet. Communications equipment is courteous enough not to listen in on messages meant for someone else.

Most packets include some kind of identifying information that tells the recipient what to do with the data. For example, a packet may bear a marker to distinguish commands from ordinary data.

The bulk of the packet is made from the data being transmitted. Packets vary in size and hence the amount of data that they may contain. Although there are no hard and fast limits, most packets range from 256 to 2048 bytes.

# **Error Handling**

Because no communication channel is error free, most packets include error detection or error correction information. The principal behind error detection is simple: include duplicate or redundant information that you can compare to the original. Because communication errors are random, they are unlikely to affect both of two copies of the transmitted data. Compare two copies sent along and if they do not match, you can be sure one of them changed during transmission and became corrupted.

Many communications systems don't rely on complex error correction algorithms as are used in storage and high quality memory systems. Communications systems have a luxury storage systems do not; they can get a second chance. If an error occurs in transmission, the system can try again—and again—until an error free copy gets through.

As a function of communication protocol, packets are part of the software standard used by the communication system. Even so, they are essential to making the hardware—the entire communication system—work properly and reliably.

# **History**

Nearly every serial communication system now uses packets of some kind. In retrospect, the idea of using packets seems natural, the logical way of organizing data. In fact, however, the concept of using packets as a method of reliably routing data

through communications systems rates as an invention with a clear-cut history. The first inkling of the concept of packet based communications dates back as early as 1960 when Paul Baran, working at RAND Corporation, conceived the idea of a redundant, packet-switched network. At the time nothing came of the idea because the chief telecommunications supplier in the United States, AT&T, regarded a communications system or network based on packets as unbuildable. AT&T preferred switching signals throughout its vast network, a technology with which the company had become familiar after nearly a century of development.

In 1965 Donald Watts Davies, working at the British National Physics Laboratory, independently conceived the idea of packetized communications, and it was he who coined the name "packet." Baran called them data blocks and his version of packet switching was "distributed adaptive message block switching." The direct ancestor of today's Internet, ARPAnet (see <u>Chapter 22</u>, "Modems"), development of which began in 1966, is usually considered the first successful packetized communication system.

# **RS-232C**

The classic serial port in your PC wears a number of different names. IBM, in the spirit of bureaucracy, sanctions an excess of syllables, naming the connection an "asynchronous data communications port." Time pressed PC users clip that to "async port" or "comm" port. Officialdom bequeaths its own term. The variety of serial link accepted by the PC industry operates under a standard called RS-232C (one that was hammered out by an industry trade group, the Electronics Industry Association or EIA), so many folks call the common serial port by its numerical specification, an RS-232C port.

So far we've discussed time in the abstract. But serial communications must occur at very real data rates, and those rates must be the same at both ends of the serial connection, if just within a frame when transmissions are asynchronous. The speed at which devices exchange serial data is called the *bit rate*, and it is measured in the number of data bits that would be exchanged in a second if bits were sent continually. You've probably encountered these bit rates when using a modem. The PC industry uses bit rates in the following sequence: 150; 300; 600; 1200; 2400; 4800; 9600; 19,200; 38,400; 57,600; and 115,200.

This sequence results from both industry standards and the design of the original IBM PC. The PC developed its serial port bit rate by using an oscillator that operates at 1.8432 MHz and associated circuitry that reduces that frequency by a factor of 1,600 to a basic operating speed of 115,200 bits per second. For this base bit rate, a device called a *programmable divider* mathematically creates the lower bit rates used by serial ports. It develops the lower frequencies by dividing the starting rate by an integer. By using a

Winn L. Rosch Hardware Bible, Electronic Edition, Chapter 21

divisor of three, for example, the PC develops a bit rate of 38,400 (that is, 115200/3). Not all available divisors are used. For example, designers never set their circuits to divide by five.

You may have noticed that some modems use speeds not included in this sequence. For example, today's popular V.34 modems operate at a base speed of 28,800 bits per second. The modem generates this data rate internally. In general, you will connect your PC to the modem so that it communicates at a higher bit rate, and the modem repackages the data to fit the data rate it uses by compressing the data or telling your PC to halt the flow of information until it is ready to send more bits.

The accepted standard in asynchronous communications allows for a number of variables in the digital code used within each data frame. When you configure any serial device and an RS-232C port, you'll encounter all of these variables: speed, number of data bits, parity choices, and number of stop bits. The most important rule about choosing which values to use is that the transmitter and receiver—your PC and the serial device— must use exactly the same settings. Think of a serial communication as being an exchange of coded messages by two spies. If the recipient doesn't use the same secret decoder ring as the sender, he can't hope to make sense out of the message. If your serial peripheral isn't configured to understand the same settings your PC sends out in its serial signals, you can't possible hope to print anything sensible.

Normally you'll configure the bit rate of the serial port on a peripheral using DIP switches or the serial peripheral's menu system. How to make the settings will vary with the serial device you are installing, so you should check its instruction manual to be sure. To use a serial port as a DOS device, you must use the DOS MODE command to set its speed and other communication parameters. This setting only affects what you print from DOS. Most programs and other operating systems take direct control of the PC's serial ports when they need them, and these program override the values set using the MODE command. You adjust the bit rates (and other serial parameters) used by your programs as part of the setup procedures of your applications or operating system. In general you should set the fastest data that both ends of your connection will allow.

# **Electrical Operation**

Serial signals have a definite disadvantage compared to parallel; bits move one at a time. At a given clock rate, fewer bits will travel through a serial link than a parallel one. The disadvantage is on the order of 12 to 1. When a parallel port moves a byte in a single cycle, a serial port take around a dozen—8 for the data bits, 1 for parity, 1 for stop, and 2 for start. That 9,600 bit-per-second serial connection actually moves text at about 800 character per second.

Compensating for this definite handicap, serial connections claim versatility. Their signals can go the distance. Not just the mile or so you can shoot out the signal from your standard serial port, but the thousands of miles you can make by modem—tied, of course, to that old serial port.

The trade-off is signal integrity for speed. As they travel down wires, digital pulses tend to blur. The electrical characteristics of wires tend to round off the sharp edges of pulses and extend their length. The farther a signal travels, the less defined it becomes until digital equipment has difficulty telling where the one pulse ends and the next begins. The more closely spaced the pulses are (and, hence, the higher the bit rate), the worse the problem becomes. By lowering the bit rate and extending the pulses and the time between them, the farther the signal can go before the pulses blend together. (Modems avoid part of this problem by converting digital signals to analog signals for the long haul. PC networks achieve length and speed by using special cables and signaling technologies.)

The question of how far a serial signal can reach depends on both the equipment and wire that you use. You can probably extend a 9,600 bps connection to a hundred feet or more. At a quarter mile, you'll probably be down to 1,200 or 300 bps (slower than even cheap printers can type).

Longer wires are cheaper with serial connections, too, a point not lost on system designers. Where a parallel cable requires 18 to 25 separate wires to carry its signals, a serial link makes do with three: one to carry signals from your PC to the serial peripheral, one to carry signals from the serial peripheral to the PC, and a common or ground signal that provides a return path for both.

The electrical signal on a serial cable is a rapidly switching voltage. Digital in nature, it has one of two states. In the communications industry, these states are termed space and mark like the polarity signals. *Space* is the absence of a bit, and *mark* is the presence of a bit. On the serial line, a space is a positive voltage, a mark is a negative voltage. In other words, when you're not sending data down a serial line, it has an overall positive voltage on it. Data will appear as a series of negative going pulses. The original design of the serial port specification called for the voltage to shift from a positive 12 volts to negative 12 volts. Because 12 volts is an uncommon potential in many PCs, the serial voltage often varies from positive 5 to negative 5 volts.

# Connectors

The physical manifestation of a serial port is the connector that glowers on the rear panel of your PC. It is where you plug your serial peripheral into your computer. And it can be the root of all evil—or so it will seem after a number of long evenings during

which you valiantly try to make your serial device work with your PC only to have text disappear like phantoms at sunrise. Again, the principal problem with serial ports is the number of options that it allows designers. Serial ports can use either of two style of connectors, each of which has two options in signal assignment. Worse, some manufacturers venture bravely in their own directions with the all-important flow control signals. Sorting out all of these options is the most frustrating part of serial port configuration.

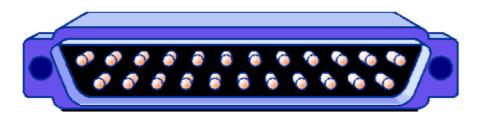

## 25-Pin

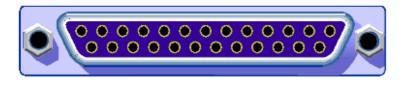

The basic serial port connector is called a 25-pin D-shell. It earns its name from having 25 connections arranged in two rows that are surrounded by a metal guide that takes the form of a rough letter D. The male variety of this connector—the one that actually has pins inside it—is normally used on PCs. Most, but hardly all, serial peripherals use the female connector (the one with holes instead of pins) for their serial ports. Although both serial and parallel ports use the same style 25-pin D-shell connectors, you can distinguish serial ports from parallel ports because on most PCs the latter use female connectors. Figure 21.3 shows the typical male serial port DB-25 connector that you'll find on the back of your PC.

#### Figure 21.3 The male DB25 connector used by serial ports on PCs.

Although the serial connector allows for 25 discrete signals, only a few of them are ever actually used. Serial systems may involve as few as three connections. At most, PC serial ports use ten different signals. Table 21.2 lists the names of these signals, their mnemonics, and the pins to which they are assigned in the standard 25-pin serial connector.

| Pin | Function        | Mnemonic |

|-----|-----------------|----------|

| 1   | Chassis ground  | None     |

| 2   | Transmit data   | TXD      |

| 3   | Receive data    | RXD      |

| 4   | Request to send | RTS      |

| 5   | Clear to send   | CTS      |

| 6   | Data set ready  | RTS      |

| 7   | Signal ground   | GND      |

Table 21.2. 25-Pin Serial Connector Signal Assignments

| 8  | Carrier detect      | CD  |

|----|---------------------|-----|

| 20 | Data terminal ready | DTR |

| 22 | Ring indicator      | RI  |

Note that in the standard serial cable, signal ground (which is the return line for the data signals on pins 2 and 3) is separated from the chassis ground on pin one. The chassis ground pin is connected directly to the metal chassis or case of the equipment, much like the extra prong of a three-wire AC power cable, and provides the same protective function. It assures that the case of the two devices linked by the serial cable are at the same potential, which means you won't get a shock if you touch both at the same time. As wonderful as this connection sounds, it is often omitted from serial cables. On the other hand, the signal ground is a necessary signal that the serial link cannot work without. You should never connect the chassis ground to the signal ground.

### 9-Pin

If nothing else, using a 25-pin D-shell connector for a serial port is a waste of at least 15 pins. Most serial connections use fewer than the complete 10; some as few as 4 with hardware handshaking, 3 with software flow control. For the sake of standardization, the PC industry sacrificed the cost of the other unused pins for years until a larger—or smaller, depending on your point of view—problem arose: space. A serial port connector was too big to fit on the retaining brackets of expansion boards along with a parallel connector. In that all the pins in the parallel connector had an assigned function, the serial connector met its destiny and got miniaturized.

The problem arose when IBM attempted to put both sorts of ports on one board inside its Personal Computer AT when it was introduced in 1984. To cope with the small space available on the card retaining bracket, IBM eliminated all the unnecessary pins but kept the essential design of the connector the same. The result was an implementation of the standard serial port that uses a 9-pin D-shell connector. To trim the 10 connections to 9, IBM omitted the little used chassis ground connection.

As with the 25-pin variety of serial connector, the 9-pin serial jack on the back of PCs uses a male connector. This choice distinguishes it from the female 9-pin D-shell jacks used by early video adapters (the MDA, CGA, and EGA systems all used this style of connector). Figure 21.4 shows the 9-pin male connector that's used on some PCs for serial ports.

Figure 21.4 The male DB-9 plug used by AT-class serial devices.

Besides eliminating some pins, IBM also rearranged the signal assignments used in the miniaturized connector. Table 21.3 lists the signal assignments for the 9-pin serial connector introduced with the IBM PC-AT.

| Pin | Function            | Mnemonic |

|-----|---------------------|----------|

| 1   | Carrier detect      | CD       |

| 2   | Receive data        | RXD      |

| 3   | Transmit data       | TXD      |

| 4   | Data terminal ready | DTR      |

| 5   | Signal Ground       | GND      |

| 6   | Data set ready      | DSR      |

| 7   | Request to send     | RTS      |

| 8   | Clear to send       | CTS      |

| 9   | Ring indicator      | RI       |

#### Table 21.3. IBM 9-Pin Serial Connector

Other than the rearrangement of signals, the 9-pin and 25-pin serial connectors are essentially the same. All the signals behave identically no matter the size of the connector on which it appears.

# **Motherboard Headers**

When a serial port is incorporated into motherboard circuitry, the motherboard maker may provide either a D-shell connector on the rear edge of the board or a header from which you must run a cable to an external connector. The pin assignments on these motherboard headers usually conforms to that of a standard D-shell connector, allowing you to use a plain ribbon cable to make the connection.

Intel, however, opts for a different pin assignment on many of its motherboards. Table 21.4 lists the pin assignments of most Intel motherboards.

#### Table 21.4. Intel Motherboard Serial Port Header Pin Assignments

Motherboard header pin Corresponding 9-Pin D-shell Pin Function

| 1  | 1             | Carrier detect      |

|----|---------------|---------------------|

| 2  | 6             | Data set ready      |

| 3  | 2             | Receive data        |

| 4  | 7             | Request to send     |

| 5  | 3             | Transmit data       |

| 6  | 8             | Clear to send       |

| 7  | 4             | Data terminal ready |

| 8  | 9             | Ring indicator      |

| 9  | 5             | Signal ground       |

| 10 | No connection | No connection       |

# **Signals**

Serial communication is an exchange of signals across the serial interface. These signals involve not just data but also the flow control signals that help keep the data flowing as fast as possible—but not too fast.

First we'll look at the signals and their flow in the kind of communication system for which the serial port was designed, linking a PC to a modem. Then we'll examine how attaching a serial peripheral to a serial port complicates matters and what you can do to make the connection work.

# **Definitions**

The names of the signals on the various lines of the serial connector sound odd in today's PC-oriented lingo because the terminology originated in the communications industry. The names are more relevant to the realm of modems and vintage teletype equipment.

Serial terminology assumes that each end of a connection has a different type of equipment attached to it. One end has a *data terminal* connected to it. In the old days when the serial port was developed, a terminal was exactly that—a keyboard and a screen that translated typing into serial signals. Today a terminal is usually a PC. For reasons known but to those who revel in rolling their tongues across excess syllables,

the term Data Terminal Equipment is often substituted. To make matters even more complex, many discussions talk about *DTE* devices—which means exactly the same thing as "data terminals."

The other end of the connection had a *data set*, which corresponds to a modem. Often engineers substitute the more formal name Data Communication Equipment or talk about *DCE* devices.

The distinction between data terminals and data sets (or DTE and DCE devices) is important. Serial communications were originally designed to take place between one DTE and one DCE, and the signals used by the system are defined in those terms. Moreover, the types of RS-232C serial devices you wish to connect determine the kind of cable you *must* use.

### **Transmit Data**

The serial data leaving the RS-232C port is called the *transmit data* line, which is usually abbreviated TXD. The signal on it comprises the long sequence of pulses generated by the UART in the serial port. The data terminal sends out this signal, and the data set listens to it.

### **Receive Data**

The stream of bits going the other direction—that is, coming in from a distant serial port—goes through the receive data line (usually abbreviated RXD) to reach the input of the serial port's UART. The data terminal listens on this line for the data signal coming from the data set.

## **Data Terminal Read**

When the data terminal is able to participate in communications, that is, it is turned on and in the proper operating mode, it signals its readiness to the data set by applying a positive voltage to the *data terminal ready* line, which is abbreviated as DTR.

# **Data Set Ready**

When the data set is able to receive data, that is, it is turned on and in the proper operating mode, it signals its readiness by applying a positive voltage to the *data set ready* line, which is abbreviated as DSR. Because serial communications must be two way, the data terminal will not send out a data signal unless it sees the DSR signal coming from the data set.

### **Request To Send**

When the data terminal is on and capable of receiving transmissions, it puts a positive voltage on its *request to send* line, usually abbreviated RTS. This signal tells the data set that it can send data to the data terminal. The absence of an RTS signal across the serial connection will prevent the data set from sending out serial data. This allows the data terminal to control the flow of the data set to it.

### **Clear To Send**

The data set, too, needs to control the signal flow from the data terminal. The signal it uses is called *clear to send*, which is abbreviated CTS. The presence of the CTS in effect tells the data terminal that the coast is clear and the data terminal can blast data down the line. The absence of a CTS signal across the serial connection prevents the data terminal from sending out serial data.

### **Carrier Detect**

The serial interface standard shows its roots in the communication industry with the *carrier detect* signal, which is usually abbreviated CD. This signal gives a modem, the typical data set, a means of signaling to the data terminal that it has made a connection with a distant modem. The signal says that the modem or data set has detected the carrier wave of another modem on the telephone line. In effect, the carrier detect signal gets sent to the data terminal to tell it that communications are possible. In some systems, the data terminal must see the carrier detect signal before it will engage in data exchange. Other systems simply ignore this signal.

# **Ring Indicator**

Sometimes a data terminal has to get ready to communicate even before the flow of information begins. For example, you might want to switch your communications program into answer mode so that it can deal with an incoming call. The designers of the serial port provided such an early warning in the form of the *ring indicator* signal, which is usually abbreviated RI. When a modem serving as a data set detects ringing voltage—the low frequency, high voltage signal that makes telephone bells ring—on the telephone line to which it is connected, it activates the RI signal, which alerts the data terminal to what's going on. Although useful in setting up modem communications, you can regard the ring indicator signal as optional because its absence usually will not prevent the flow of serial data.

# **Signal Ground**

All of the signals used in a serial port need a return path. The signal ground provides this return path. The single ground signal is the common return for all other signals on the serial interface. Its absence will prevent serial communications entirely.

# **Flow Control**

This hierarchy of signals hints that serial communications can be a complex process. The primary complicating factor is handshaking or flow control. The designers of the serial interface recognized that some devices might not be able to accommodate information as fast as others could deliver it, so they built handshaking into the serial communications hardware using several special control signals to compensate.

This flow control signal become extremely important when you want to use a serial connection to a slow device such as a plotter. Simply put, plotters aren't as quick as PCs. As you sit around playing Freecell for the fourteenth hand while waiting for the blueprint of your dream house to roll out, that news comes as little surprise. Plotters are mechanical devices that work at mechanical speed. PCs are electronic roadrunners. A modern PC can draw a blueprint in its memory much quicker than your plotter can ink it on paper.

The temptation for your PC is to force feed serial devices, shooting data out like rice

puffs from a cannon. After the first few gulps, however, force fed serial devices choke. With a serial connection, the device might let the next salvo whiz right by. Your plotter may omit something important—like bedroom walls and bathroom plumbing—and leave large gaps in your plan (but, perhaps, making your future life somewhat more interesting). Flow control helps throttle down the onslaught of data to prevent such omissions.

The concept underlying flow control is the same as for parallel and other ports: your peripheral signals when it cannot accept more characters to stop the flow from your PC. When the peripheral is ready for more, it signals its availability to your PC. Where the traditional parallel port uses a simple hardware scheme of this handshaking, flow control for the serial port is a more complex issue. As with every other aspect of serial technology, flow control is a theme overwhelmed by variations.

The chief division in serial flow control is between hardware and software. *Hardware flow control* involves the use of special control lines that can be (but don't have to be) part of a serial connection. Your PC signals whether it is ready to accept more data by sending a signal down the appropriate wire. *Software flow control* involves the exchange of characters between PC and serial peripheral. One character tells the PC your peripheral is ready and another warns that it can't deal with more data. Both hardware and software flow control take more than one form. As a default, PC serial ports use hardware flow control (or hardware handshaking). Most serial peripherals do, too.

## **Hardware Flow Control**

Several of the signals in the serial interface are specifically designed to help handle flow control. Rather than a simple on and off operation, however, they work together in an elaborate ritual.

The profusion of signals seems overkill for keeping a simple connection such as that with a plotter under control, and it is. The basic handshaking protocol for a serial interface is built around the needs of modem communications. Establishing a modem connection and maintaining the flow of data through it is one of the more complex flow control problems for a serial port. Even a relatively simple modem exchange involves about a dozen steps with a complex interplay of signals. The basic steps of the dance would go something like this:

1. The telephone rings when a remote modem wants to make a connection. The data set sends the ring indicator signal to the data terminal to warn of the incoming call.

- 2. The data terminal switches on or flips into the proper mode to engage in communications. It indicates its readiness by sending the data terminal ready signal to the data set.

- 3. Simultaneously, it activates its request to send line.

- 4. When the data set knows the data terminal is ready, it answers the phone and listens for the carrier of the other modem. If it hears the carrier, it sends out the carrier detect signal.

- 5. The data set negotiates a connection. When it is capable of sending data down the phone line, it activates the data set ready signal.

- 6. Simultaneously, it activates its clear to send line.

- 7. The data set relays bytes from the phone line to the data terminal through the receive data line.

- 8. The data terminal sends bytes to the data set (and thence the distant modem) through the transmit data line.

- 9. Because the phone line is typically slower than the data terminal-to-data set link, the data set quickly fills its internal buffer. It tells the data terminal to stop sending bytes by deactivating the clear to send line. When its buffer empties, it reactivates clear to send.

- 10. If the data terminal cannot handle incoming data, it deactivates its request to send line. When it can again accept data, it reactivates the request to send line.

- 11. The call ends. The carrier disappears, and the data set discontinues the carrier detect signal, clear to send signal, and data set ready signal.

- 12. Upon losing the carrier detect signal, the data terminal returns to its quiescent state, dropping its request to send and data terminal ready signals.

Underlying the serial dance are two rules. 1. The data terminal must see the data set ready signal as well as the clear to send signal before it will disgorge data. 2. The data set must see the data terminal ready and request to send signals before it will send out serial data. Interrupting either of the first pair of signals will usually stop the data terminal from pumping out data. Interrupting either of the second pair of signals will stop the data set from replying with its own data.

The carrier detect signal may or may not enter into the relationship. Some data terminals require seeing the carrier detect signal before they will transmit data. Others just don't give a byte one way or the other.

## **Software Flow Control**

The alternate means of handshaking, software flow control, requires your serial peripheral and PC to exchange characters or tokens to indicate whether they should transfer data. The serial peripheral normally sends out one character to indicate it can accept data and a different character to indicate that it is busy and cannot accommodate more. Two pairs of characters are often used, XON/XOFF and ETX/ACK.

In the XON/XOFF scheme, the XOFF character sent from your serial peripheral tells your PC that its buffer is full and to hold off sending data. This character is also sometimes called DC1 and has an ASCII value of 19 or 013(Hex). It is sometimes called Control-S. (With some communications programs, you can hold down the Control key and type S to tell the remote system to stop sending characters to your PC). Once your serial peripheral is ready to receive data again, it sends out XON, also known as DC3, to your PC. This character has an ASCII value of 17 or 011(Hex). It is sometimes called Control-Q. When you hold down Control and type Q into your communications program, it cancels the effect of a Control-S.

ETX/ACK works similarly. ETX, which is an abbreviation for End TeXt tells your PC to hold off on sending more text. This character has an ASCII value of 3 (decimal or hexadecimal) and is sometimes called Control-C. ACK, short for Acknowledge, tells your PC to resume sending data. It has an ASCII value of 6 (decimal or hexadecimal), and is sometimes called Control-F.

There's no issue as to whether hardware or software flow control is better. Both work and that's all that's necessary. The important issue is what kind of flow control your serial peripheral and software use. You must assure that your PC, your software, and your serial peripheral use the same kind of flow control.

Your software will either tell you what it prefers or give you the option of choosing when you load the driver for your peripheral. On your serial peripheral, you select serial port flow control when you set it up. Typically, this will involve making a menu selection or adjusting a DIP switch.

# Cables

The design of the standard RS-232C serial interface anticipates that you will connect a data terminal to a data set. When you do, all the connections at one end of the cable that links them are carried through to the other end, pin for pin, connection for connection. The definitions of the signals at each end of the cable are the same, and the function and

direction of travel (whether from data terminal to data set or the other way around) of each is well defined. Each signal goes straight through from one end to the other. Even the connectors are the same at either end. Consequently, a serial cable should be relatively easy to fabricate.

In the real world, nothing is so easy. Serial cables are usually much less complicated or much more complicated than this simple design. Unfortunately, if you plan to use a serial connection for a printer or plotter, you have to suffer through the more complex design.

# **Straight Through Cables**

Serial cables are often simpler than pin-for-pin connections from one end to the other because no serial link uses all 25 connector pins. Even with the complex handshaking schemes used by modems, only nine signals need to travel from the data terminal to the data set, PC to modem. (For signaling purposes, the two grounds are redundant—most serial cables do not connect the chassis ground.) Consequently, you need only make these 9 connections to make virtually any data terminal to data set link work. Assuming you have a 25-pin D-shell connector at either end of your serial cable, the essential pins that must be connected are 2 through 8, 20, and 22 on a 25-pin D-shell connector. With 9-pin connectors at either end of your serial cable, all 9 connections are essential.

Not all systems use all the handshaking signals, so you can often get away with fewer connections in a serial cable. The minimal case is a system that uses software handshaking only. In that case, you need only three connections: transmit data, receive data, and the signal ground. In other words, you need only connect pins 2, 3, and 7 on a 25-pin connector or pins 2, 3, and 5 on a 9-pin serial connector—providing, of course, you have the same size connector at each end of the cable.

Although cables with an intermediate number of connections are often available, they are not sufficiently less expensive than the nine-wire cable to justify the risk and lack of versatility. So you should limit your choices to a nine-wire cable for systems that use hardware handshaking or three-wire cables for those that you're certain use only software flow control.

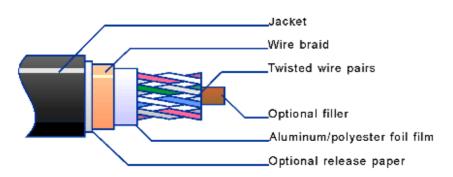

Manufacturers use a wide range of cable types for serial connections. For the relatively low data rates and reasonable lengths of serial connections, you can get away with just about everything, including twisted pair telephone wire. To ensure against interference, you should use shielded cable, which wraps a wire braid or aluminum coated plastic film about inner conductors to prevent signals leaking out or in. The shield of the cable should be connected to the signal ground. (Ideally, the signal ground should have its own wire, and the shield should be connected to chassis ground, but most folks just don't bother.)

## **Adapter Cables**

If you need a cable with a 25-pin connector at one end and a 9-pin connector at the other, you cannot use a straight through design even when you want to link a data terminal to a data set. The different signal layouts of the two styles of connector are incompatible. After all, you can't possibly link pin 22 on a 25-pin connector to a non-existent pin 22 on a 9-pin connector.

This problem is not uncommon. Even though the 9-pin connector has become a *de facto* standard on PCs, most other equipment, including serial plotter, printers and modems, has stuck with the 25-pin standard. To get from one connector type to another, you need an adapter. The adapter can take the form of a small assembly with a connector on each end or of an adapter cable, typically from six inches to six feet long.

Although commercial adapters are readily available, you can easily make your own. Table 21.5 shows the proper wiring for an adapter to link a 25-pin serial device to a 9pin jack on a PC, assuming a data terminal-to-data set connection.

| 25-pin connector | 9-pin connector | Mnemonic | Function            |

|------------------|-----------------|----------|---------------------|

| 2                | 3               | TXD      | Transmit data       |

| 3                | 2               | RXD      | Receive data        |

| 4                | 7               | RTS      | Request to send     |

| 5                | 8               | CTS      | Clear to send       |

| 6                | 6               | RTS      | Data set ready      |

| 7                | 5               | GND      | Signal ground       |

| 8                | 1               | CD       | Carrier detect      |

| 20               | 4               | DTR      | Data terminal ready |

| 22               | 9               | RI       | Ring indicator      |

Table 21.5. Wiring for 9-to-25 Pin Serial Port Adapter

Again, nine wires in a cable will suffice. For systems using only software flow control, you need link only the three essential pins. Note, however, the three pins do not get connected one-for-one. Pin 2 on the 25-pin connector goes to pin 3 on the 9-pin; pin 3 on the 25-pin goes to pin 2 on the 9-pin. The ground on pin 7 of the 25-pin connector

goes to pin 5 of the 9-pin connector.

# **Crossover Cables**

As long as you want to connect a computer serial port that functions to a modem, you should have no problem with serial communications. You will be connecting a data terminal to a data set, exactly what engineers designed the serial systems for. Simply sling a cable with enough conductors to handle all the vital signals between the computer and modem and, *Voila!* Serial communications without a hitch. Try it, and you're likely to wonder why so many people complain about the capricious nature of serial connections.

When you want to connect a plotter or printer to a PC through a serial port, however, you will immediately encounter a problem. The architects of the RS-232C serial system decided that both PCs and the devices are data terminals or DTE devices. The designations actually made sense, at least at that time. You were just as likely to connect a serial printer (such as a teletype) to a modem as you were a computer terminal. There was no concern about connecting a printer to a PC because PCs didn't even exist back then.

When you connect a plotter or printer and your PC—or any two DTE devices—with an ordinary serial cable, you will not have a communication system at all. Neither machine will know that the other one is even there. Each will listen on the serial port signal line that the other is listening to, and each will talk on the line that the other talks on. One device won't hear a bit the other is saying.

The obvious solution to the problem is to switch some wires around. Move the transmit data wire from the PC to where the receive data wire goes on the plotter or printer. Route the PC's receive data wire to the transmit data wire of the plotter or printer. A simple *crossover cable* does exactly that, switching the transmit and receive signals at one end of the connection.

Many of the device that you plug into a PC are classed as DTE or data terminals just like the PC. All of these require a crossover cable. Table 21.6. lists many of the device you might connect to your PC and whether they function as data terminals (DTE) or data sets (DCE).

#### Table 21.6. Common Serial Device Types

|  | Peripheral | Device type | Cable needed to connect to PC |

|--|------------|-------------|-------------------------------|

|--|------------|-------------|-------------------------------|

| PC             | DTE | Crossover        |

|----------------|-----|------------------|

| Modem          | DCE | Straight-through |

| Mouse          | DCE | Straight-through |

| Trackball      | DCE | Straight-through |

| Digitizer      | DCE | Straight-through |

| Scanner        | DCE | Straight-through |

| Serial printer | DTE | Crossover        |

| Serial plotter | DTE | Crossover        |

Some serial ports on PCs (and some serial devices, too) offer a neat solution to this problem. They allow you to select whether they function as DTE or DCE with jumpers or DIP switches. To connect one of these to a plotter or printer using an ordinary straight through cable, configure the PC's serial port as DCE.

This simple three-wire crossover cable works if you plan on using only software flow control. With devices that require hardware handshaking, however, the three-wire connection won't work. You need to carry the hardware handshaking signals through the cable. And then the fun begins.

Your problems begin with carrier detect. The carrier detect signal originates on a data set, and many data terminals need to receive it before they send out data. When you connect two data terminals, neither generates a signal anything like carrier detect, so there's nothing to connect to make the data terminals start talking. You have to fabricate the carrier detect signal somehow.

Because data terminals send out their data terminal ready signals whenever they are ready to receive data, you can steal the voltage from that connection. Most crossover cables link their carrier detect signals to the data terminal ready signal from the other end of the cable.

Both data terminals will send out their data terminal ready signals when they are ready. They expect to see a ready signal from a data set on the data set ready connection. Consequently, most crossover cables also link data terminal ready on one end to data set ready (as well as carrier detect) at the other end. Making this linkup allows the two data terminals at either end of the cable to judge when the other is ready.

The actual flow control signals are request to send and clear to send. The typical crossover cable thus links the request to send signal from one end to the clear to send connection at the other end. This link will enable flow control—providing, of course, the two data terminal devices follow the RS-232C signaling standard. Table 21.7 shows summarizes these connections.

| PC end | Function            | Device end |

|--------|---------------------|------------|

| 2      | Transmit data       | 3          |

| 3      | Receive data        | 2          |

| 4      | Request to send     | 5          |

| 5      | Clear to send       | 4          |

| 6      | Data set ready      | 20         |

| 7      | Signal ground       | 7          |

| 8      | Carrier detect      | 20         |

| 20     | Data terminal ready | 6          |

| 20     | Data terminal ready | 8          |

# Table 21.7. Basic Crossover Cable for Hardware Handshaking (25-Pin<br/>Connectors)

Unfortunately, this cable may not work properly when you link many serial devices to the typical PC. A different design that combines the request to send and clear to send signals and links them to carrier detect at the opposite end of the cable often works better than the above by-the-book design. The wiring connections for this variety of crossover cable are listed in Table 21.8.

### Table 21.8. Wiring for a Generic Crossover Serial Cable (25-Pin Connectors)

*PC end Function Device end* 2 Transmit data 3 3 Receive data 2 4 Request to send 8 5 Clear to send 8 6 Data set ready 20 7 Signal ground 7 8 Carrier detect 5 8 Carrier detect 4 20 Data terminal ready 22 20 Data terminal ready 6 22 Ring indicator 20

A number of printers vary from the signal layout ascribed to RS-232C connections and use different connections for flow control. DEC serial printers, among others, use pin 19 instead of pin 20 for hardware flow control. These require another variation on the generic crossover cable to make them work properly with PCs. The proper wiring is shown in Table 21.9.

# Table 21.9. Wiring for Crossover Serial Cable (25-Pin to 25-Pin) for DEC PrintersUsing Pin 19 Handshake

| PC end | Function | Device end |

|--------|----------|------------|

|        |          |            |

| 2  | Transmit data       | 3  |

|----|---------------------|----|

| 3  | Receive data        | 2  |

| 4  | Request to send     | 8  |

| 5  | Clear to send       | 8  |

| 6  | Data set ready      | 19 |

| 7  | Signal ground       | 7  |

| 8  | Carrier detect      | 5  |

| 8  | Carrier detect      | 4  |

| 20 | Data terminal ready | 22 |

| 20 | Data terminal ready | 6  |

Some of the newer and more popular serial printers are in the LaserJet series made by Hewlett-Packard. These use a simplified hardware flow control system that involves only the DTR signal on the printer end of the cable. Earlier printer models use 25-pin connectors, and Hewlett-Packard sells a crossover cable for these as its part number 17255D. Its wiring is shown in Table 21.10.

| PC end | LaserJet end   |     |                     |

|--------|----------------|-----|---------------------|

| Pin    | Signal         | Pin | Signal              |

| 1      | Chassis ground | 1   | Chassis ground      |

| 2      | Transmit data  | 3   | Receive data        |

| 3      | Receive data   | 2   | Transmit data       |

| 5      | Clear to send  | 20  | Data terminal ready |

| 6      | Data set ready | 20  | Data terminal ready |

| 7      | Signal ground  | 7   | Signal ground       |

You can directly connect a PC-style 9-pin serial port to a LaserJet with a 25-pin serial connector using Hewlett-Packard's adapter cable model 2424G. Its wiring is shown in Table 21.11.

### Table 21.11. HP 9-Pin to 25-Pin Serial Adapter Cable

PC end

LaserJet end

| Pin | Signal         | Pin | Signal              |

|-----|----------------|-----|---------------------|

| 2   | Receive data   | 2   | Transmit data       |

| 3   | Transmit data  | 3   | Receive data        |

| 5   | Signal ground  | 7   | Signal ground       |

| 6   | Clear to send  | 20  | Data terminal ready |

| 8   | Data set ready | 20  | Data terminal ready |

More recent LaserJets use 9-pin serial connectors instead of the 25-pin variety. The machines do not follow the IBM 9-pin standard used by the 9-pin jacks on PCs but instead use its complement. If you consider the IBM-style connector DTE, then the Hewlett-Packard LaserJet 9-pin connector is DCE. It requires its own adapter cable to plug into standard 25-pin PC-style serial ports. The necessary adapter cable is available from Hewlett-Packard as model number C2933A. Table 21.12 shows its wiring.

Table 21.12. HP 25-Pin to 9-Pin Serial Adapter Cable

| PC end | LaserJet end        |     |                     |

|--------|---------------------|-----|---------------------|

| Pin    | Signal              | Pin | Signal              |

| 2      | Transmit data       | 3   | Receive data        |

| 3      | Receive data        | 2   | Transmit data       |

| 4      | Request to send     | 7   | Not used            |

| 5      | Clear to send       | 8   | Data terminal ready |

| 6      | Data set ready      | 6   | Data terminal ready |

| 7      | Signal ground       | 5   | Signal ground       |

| 8      | Carrier detect      | 1   | Request to send     |

| 20     | Data terminal ready | 4   | Data set ready      |

| 22     | Ring indicator      | 9   | Not used            |

The Hewlett-Packard redefinition of the 9-pin serial connector for its printers has one big benefit. You can connect a 9-pin PC serial port directly to a 9-pin HP printer port using a straight through cable. Moreover, only HP's printers use only seven of the nine connections. Table 21.13 shows the wiring of this cable, which is available from Hewlett-Packard as its model C2932A.

### Table 21.13. HP 9-Pin to 9-Pin Serial Adapter Cable

| PC end | LaserJet end        |     |                     |

|--------|---------------------|-----|---------------------|

| Pin    | Signal              | Pin | Signal              |

| 1      | Carrier Detect      | 1   | Carrier detect      |

| 2      | Receive data        | 2   | Transmit data       |

| 3      | Transmit data       | 3   | Receive data        |

| 4      | Data terminal ready | 4   | Data set ready      |

| 5      | Signal ground       | 5   | Signal ground       |

| 6      | Clear to send       | 6   | Data terminal ready |

| 7      | Request to send     | 7   | Not used            |

| 8      | Data set ready      | 8   | Data terminal ready |

| 9      | Ring indicator      | 9   | Not used            |

One way to avoid the hassle of finding the right combination of hardware handshaking connections would appear to be letting software do it—avoiding hardware handshaking and instead using the XON-XOFF software flow control available with most serial devices. Although a good idea, even this expedient can cause hours of head scratching when nothing works as it should—or nothing works at all.

When trying to use software handshaking, nothing happening is a common occurrence. Without the proper software driver, your PC or PS/2 has no idea that you want to use software handshaking. It just sits around waiting for a DSR and a CTS to come rolling in toward it from the connected serial device.

You can sometimes circumvent this problem by connecting the data terminal ready to data set ready and request to send to clear to send within the connectors at each end of the cable. This wiring scheme satisfies the handshaking needs of a device with its own signals. But beware. This kind of subterfuge will make systems that use hardware handshaking print, too, but you'll probably lose large blocks of text when the lack of real handshaking lets your PC continue to churn out data even after your printer shouts "Stop!"

Finally, note that some people call crossover cables *null modem cables*. This is not correct. A null modem is a single connector used in testing serial ports. It connects the transmit data line to the receive data line of a serial port as well as crossing the handshaking connections within the connector. Correctly speaking, a null-modem cable is equipped with this kind of wiring at both ends. It forces both serial ports constantly on and prevents any hardware flow control from functioning at all. Although such a cable can be useful, it is not the same as a crossover cable. Substituting one for the other will lead to some unpleasant surprises—text dropping from sight from within documents as mysteriously and irrecoverably as D. B. Cooper.

## **UARTs**

A serial port has two jobs to perform. It must re-package parallel data into serial form, and it must send power down a long wire with another circuit at the end, which is called driving the line.

Turning parallel data into serial is such a common electrical function that engineers created special integrated circuits that do exactly that. Called *Universal Asynchronous Receiver/Transmitter* chips or UARTs, these chips gulp down a byte or more of data and stream it out a bit at a time. In addition, they add all the other accouterments of the serial signal—the start, parity, and stop bits. Because every serial practical connection is bi-directional, the UART works both ways, sending and receiving, as its name implies.

Because the UART does all the work of serializing your PC's data signals, its operation is one of the limits on the performance of serial data exchanges. PCs have used three different generations of UARTs, each of which imposes its own constraints.

The choice of chip is particularly critical when you connect your serial port to modem to it. When you communicate on-line with a modem, you're apt to receive long strings of characters through the connection. Your PC must take each character from a register in the UART and move it into memory. When your PC runs a multitasking system, it may be diverted for several milliseconds before it turn its attention to the UART and gathers up the character. Older UARTs must wait for the PC to take away one character before they can accept another from the communications line. If the PC is not fast enough, the characters pile up. The UART doesn't know what to do with them, and some of the characters simply get lost. The latest UARTs incorporate small buffers, or memory areas, that allow the UART to temporarily store characters until the PC has time to take them away. These newer UARTs are more immune to character loss and are preferred by modem users for high speed communications.

When you connect a printer to a serial port, you don't have such worries. The printer connection is more a monologue than a dialogue—your PC chatters out characters and gets very little backtalk from your printer. Typically, it will get only a single XOFF or XON character to tell the PC to stop or start the data flow. Because there's no risk of a pileup of inbound characters, there's no need for a buffer in the UART.

If you have both a modem and a serial printer attached to your PC, your strategy should be obvious; the modem gets the port with the faster UART. Your printer can work with whatever UART is left over.

The three UART chips that PC and peripheral makers install in their products are the

8250, 16450, and 16550A.

#### 8250

The first UART used in PCs was installed in the original IBM PC's Asynchronous Communications Adapter card in 1981. Even after a decade and a half, it is still popular on inexpensive port adapter expansion boards because it is cheap. It has a one-byte internal buffer that's exactly what you need for printing or plotting applications. It can hold the XOFF character until your PC gets around to reading it. It is inadequate for reliable two way communications at high modem speeds.

### **16450**

In 1984, designers first put an improved version of the 8250, the 16450 UART, in PCs. Although the 16450 has a higher speed internal design, it still retains the one-byte buffer incorporated into its predecessor. Serial ports built using it may still drop characters under some circumstances at high data rates. Although functionally identical, the 16450 and 8250 are physically different (they have different pin-outs), and you cannot substitute one in a socket meant for the other.

### 16550A

The real UART breakthrough came with the introduction of the 16550 to PCs in 1987. The first versions of this chip proved buggy, so it was quickly revised to produce the 16550A. It is commonly listed as 16550AF and 16550AFN, with the last initials indicating the package and temperature rating of the chip. The chief innovation incorporated into the 166550 was a 16-byte *first-in, first out buffer* (or FIFO). The buffer is essential to high speed modem operating in multitasking systems, making this the chip of choice for communications.

To maintain backward compatibility with the 16450, the 16550 ignores its internal buffer until it is specifically switched on. Most communications programs activate the buffer automatically. Physically, the 16550 and 16450 will fit and operate in the same sockets, so you can easily upgrade the older chip to the newer one.

# **Register Function**

The register at the base address assigned to each serial port is used for data communications. Bytes are moved to and from the UART using the microprocessor's OUT and IN instructions. The next six addresses are used by other serial port registers, in order: the Interrupt Enable Register, the Interrupt Identification Register, the Line Control Register, the Modem Control Register, the Line Status Register, and the Modem Status Register. Another register, called the Divisor Latch, shares the base address used by the Transmit and Receive registers and the next higher register used by the interrupt enable register. It is accessed by toggling a setting in the line control register.

This latch stores the divisor that determines the operating speed of the serial port. Whatever value is loaded into the latch is multiplied by 16. The resulting product is used to divide the clock signal supplied to the UART chip to determine the bit rate. Because of the factor of 16 multiplication, the highest speed the serial port can operate at is limited to 1/16 the supplied clock (which is 1.8432 MHz). Setting the latch value to its minimum, one, results in a bit rate of 115,200.

Registers not only store the values used by the UART chip but also are used to report to your system how the serial conversation is progressing. For example, the line status register indicates whether a character that has been loaded to be transmitted has actually been sent. It also indicates when a new character has been received.

Although you can change the values stored in these registers manually using Debug or your own programs, for the most part you'll never tangle with these registers. They do, however, provide flexibility to the programmer.

Instead of being set with DIP switches or jumpers, the direct addressability of these registers allows all the vital operating parameters to be set through software. For instance, by loading the proper values into the line control register, you alter the word length, parity, and number of stop bits used in each serial word.

# **Buffer Control**

Operating system support for the buffer in the 16550 appeared only with Windows 3.1. Even then it was limited in support to Windows applications only. DOS applications require internal FIFO support even when they run inside Windows 3.1. Windows for Workgroups (Version 3.11) extended buffer support to DOS applications running within the operating environment. The standard communications drivers for OS/2 Warp

and Windows 95 operating systems will automatically take advantage of the 16550 buffer when the chip is present.

Windows 3.1 uses its COMM.DRV for controlling the buffer of the 16650. You control whether the buffer is activated by altering the COMxFIFO entries for each of your serial ports in the [386Enh] Section of your SYSTEM.INI file of any member of the Window 3.1 family. To activate the buffer for a specific port, set COMxFIFO to one where the *x* is the port designation. To deactivate the buffer, make the entry zero. For example, the following entries in SYSTEM.INI will switch on the buffer for COM3 only:

[386Enh] COM1FIFO=0 COM2FIFO=1 COM3FIFO=0 COM4FIFO=0

By default, Windows will activate the buffers in any 16550 chip that it finds.

Under Windows 95, you can control the FIFO buffer through the Device Manager section of the System folder found in Control Panel. Once you open Control Panel, click on the System icon. Click on the Device Manager tab, then the entry for Ports, which will then expand to list the ports available in your system. Click on the COM port you want to control, then click on the Properties button below the listing, as shown in Figure 21.5.

### Figure 21.5 Windows 95 Device Manager folder.

From the Communications properties screen, click on the Port Settings tab. In addition to the default parameters set up for your chosen port, you'll see a button labeled Advanced. Clicking on it will give you control of the FIFO buffer, as shown in Figure 21.6.

### Figure 21.6 Disabling or enabling your UART FIFO buffer under Windows 95.